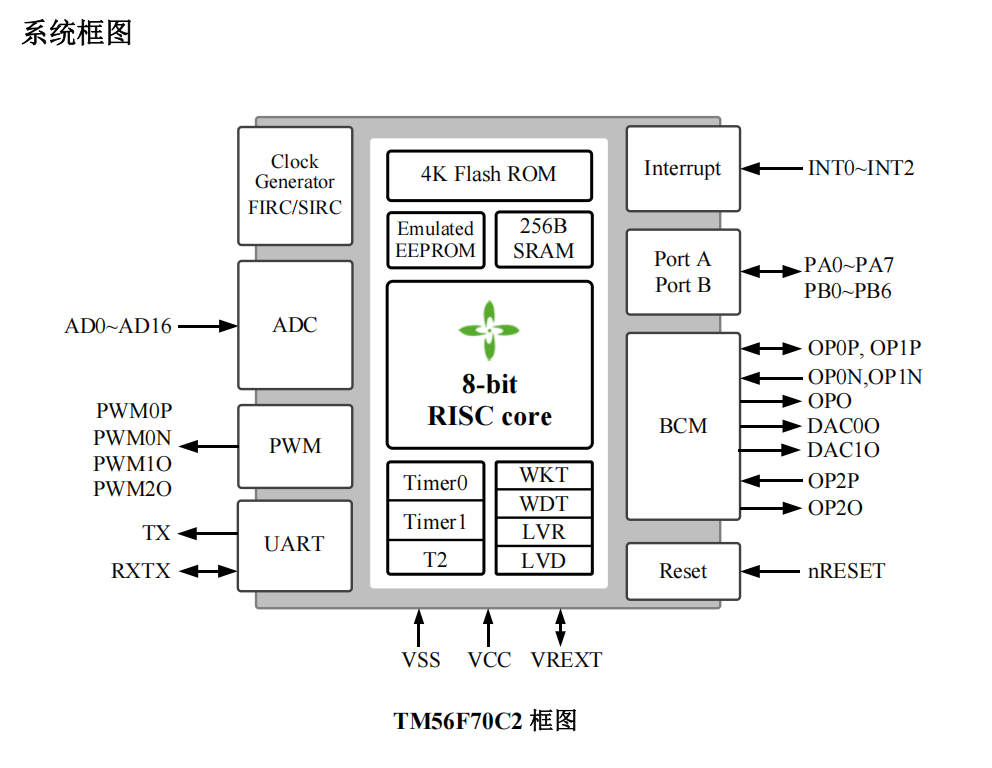

TM56F70C2

特性

1. ROM: 4K*16 bits Flash, 内置 模拟EEPROM 32*16 bits

2. RAM: 256 Bytes

3. STACK: 8 Levels

4. 系统时钟类型选择:

l 内置快速 RC 振荡器 (FIRC), 18.432 MHz

l 内置慢速 RC 振荡器 (SIRC), 37 KHz

5. 系统时钟预分频器:

l 系统时钟可分频1/2/4/8选项

6. 省电运行模式

l FAST 模式: 启用慢速时钟,快速时钟保持 CPU 运行

l SLOW 模式: 快速时钟可以禁用或启用,慢速时钟保持 CPU 运行

l IDLE 模式: 快速时钟和 系统时钟 停止。 慢速时钟保持运行

l STOP 模式: 所有时钟停止

7. 3个独立定时器

l Timer0

- 8位定时器除以1~256预分频选项/自动重载/计数器模式/中断/停止功能

l Timer1

- 8位定时器除以1~256预分频选项/自动重载/中断/停止功能

l T2

- IDLE 模式唤醒定时器或用作一个简单的 15 位时基定时器

- 4 个中断间隔时间选项

- 时钟源: 慢速时钟、Fsys/128 或 FIRC/512 (18.432MHz/512)

8. 中断 (Interrupt)

l 3个外部中断引脚

- 1 引脚下降沿唤醒触发和中断

- 2个引脚上升沿或下降沿唤醒触发和中断

l Timer0 / Timer1 / T2 / Wake-up 定时器中断

l ADC 中断

l PWM 中断

l UART 中断

l LVD 中断

9. Wake-up 定时器(WKT)

l 由内置 SIRC 振荡器提供时钟,具有 4 个可调节中断时间

- 28 ms / 55 ms / 111 ms / 221 ms @VCC=5V

10. Watchdog 定时器 (WDT)

l 由内置 SIRC 振荡器提供时钟,具有 4 个可调节复位时间

- 221 ms /443 ms /1771 ms /3542 ms @VCC=5V

11. 三个 16位PWM

l 独立的 PWM 占空比

l 共享 PWM 周期

l PWM时钟源:系统时钟 (Fsys)或FIRC(18.432MHz)或FIRC*2(36.864MHz)

l PWM0支持互补输出 (PWM0P、PWM0N) 与非重叠输出选项

12. 12 位 ADC,具有 17 个外部引脚输入通道 和 7 个内部电压通道

l 内部电压通道:VR, OPA2TOADC, VTEMP, LDO1.2V, VSS, VCC/201, VCC/4

l ADC参考电压:VCC或VR或LDO1.2V

13. BCM

l 14位DAC0和比较器OPA0,用于恒流控制

l 14位DAC1和比较器OPA1,用于恒压控制

l OPA2 为1/10/20/50倍放大器

14. UART

l 波特率(Baud rate) 最高可达到115200

l 支持 单线模式

15. 复位 (Reset)

l 上电复位 (POR)

l 低电压复位 (LVR)

l 外部引脚复位 (XRST)

l 看门狗计时器复位(WDTR)

16. 低电压复位(LVR)和低电压检测(LVD)

l 16级低电压复位:2.13V ~ 4.26V,可禁用

l 15级低电压检测:2.24V~4.20V,可禁用,带迟滞(hysteresis)选项

17. 工作电压 : 2.2V~5.5V

*上电 VCC 必须超过 POR 2.0V 和用户选择的 LVR 电平,请参阅“电气特性图”以避免进入 ROM 死区。

18. 工作温度 : -40°C to + 105°C

19. 16位ROM数据查表

20. 16 位循环冗余校验 (CRC) 功能

21. 指令集: 39 个指令

22. I/O ports:

l 15 个GPIO

- 开漏输出(Open-Drain Output)

- CMOS 推挽输出(CMOS Push-Pull Output)

- 具有上拉/下拉电阻选项的施密特触发器输入

- 所有 I/O 均具有 High-Sink

- 1/2 VCC (1/2 bias) 输出

- 支持唤醒功能

23. 编程连接支持 4 线 (ICP) 或 6 线编程

24. 封装类型:

l 20-pin SOP (300 mil)

l 20-pin TSSOP (173 mil)

l 20-pin QFN20 (3*3*0.75-0.4mm)

l 16-pin SOP (150 mil)

25. 片上调试 / ICE 接口

l 使用2线专用ICE引脚,不占用GPIO